UART串口通信

UART通信原理

- UART(universal asynchronous receiver-transmitter)异步收发传输器是一种采用异步串行通信方式的通用异步收发传输器;它在发送数据时将并行数据转换成串行数据来传输,在接收数据时将接收到的串行数据转换成并行数据。它包含RS232,RS499,RS423,RS485等接口标准规范和总线标准规范。

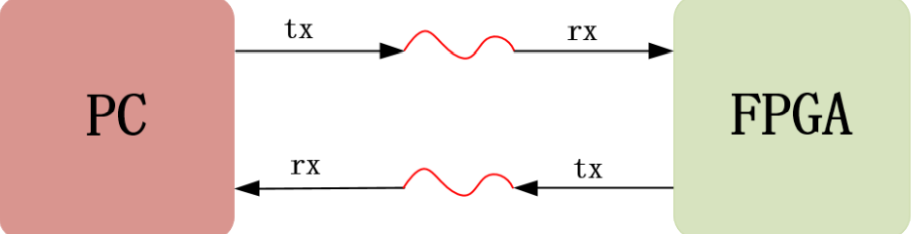

- UART串口通信需要两根信号线来实现,一根用于发送,另外一根接收。

- UART可以实现全双工,即可以同时进行发送数据和接收数据。

优缺点

- 缺点:

- 传输距离不远,速率相对较慢

- 优点:

- 很多传感器芯片或CPU都带有串口功能,目的是在使用一些传感器或CPU时可以通过串口进行调试。

- 在较为复杂的高速数据接口和数据链路集合的系统中往往联合调试比较困难,可以先使用串口数据链路部分验证后,再把串口换成高速数据接口。

- 串口的数据线一共两根,没有时钟线,节省了大量的管脚资源。

1. 协议层:通信协议(包括数据格式、传输速率等)

传输速率

串口通信的速率用波特率表示,它表示每秒传输二进制数据的位数,单位是bit/s(位/秒),简称bps;

常用的波特率有9600、19200、38400、57600以及115200等

比特率和波特率既有联系,又有区别。比特率描述的是数据,波特率描述的是信号。我们知道,数据是用信号来表示的。如果一个信号码元只能代表1 比特,那么波特率和比特率是相等的。如果一个码元可以表示n个比特信息,那么比特率是波特率的n倍。

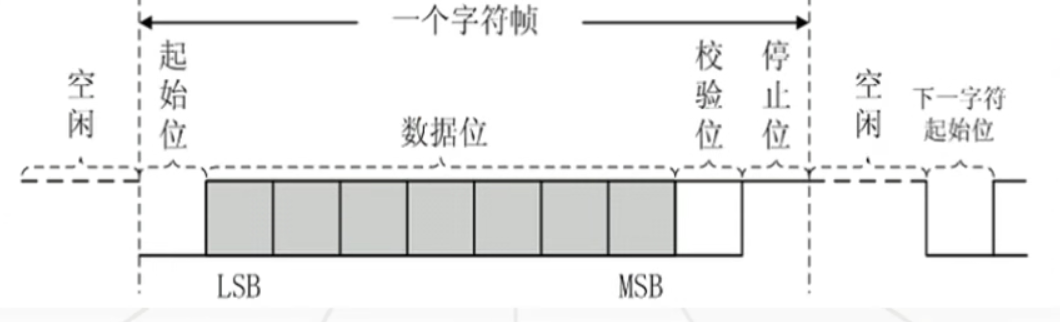

数据格式

数据格式,一帧数据由4部分构成- 起始位(1bit)

- 数据位(6/7/8bit)

- 奇偶校验位(1bit)

- 停止位(1bit\1.5bit\2bit)UART数据格式

2. 物理层:接口类型、电平标准等。

- UART通信有两根信号线,发送数据端口线TX(Transmitter),接收数据端口线RX(Receiverr),PC的TX端连接的是FPGA的RX,PC的RX端连接的是FPGA的TX。

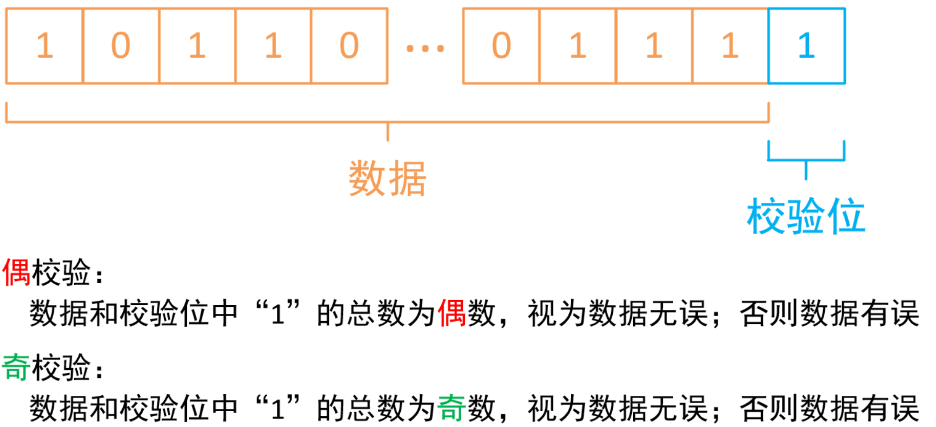

UART通信奇偶校验

- 校验位分为奇校验和偶校验,用于检验数据再传输过程中是否出错。

奇校验时,发送方应使数据位中1的个数与校验位中1的个数之和为奇数;接收方在接收数据时,对1的个数进行检查,若不为奇数,则说明数据在传输过程中出了差错。同样,偶校验则检查1的个数是否为偶数。 - 奇校验:奇偶校验是一种通信中检验数据传输正确性的方法。通常采用哪种校验方式是收发双方事先约定好的,发送端发送的数据中包括原始数据和一 bit 校验位,若是奇校验则要保证发送的数据中 1 的 bit 数是奇数个,若是偶校验,则要保证发送的数据中 0 的 bit 数是偶数个。例如:采用奇校验时,若原始数据中 1的 bit 数是奇数个,则校验位此时应该为 0,若原始数据中 1 的 bit 数是偶数个,则校验位此时应该为 1;反之亦然。

1.UART通信奇偶校验-输入数据的校验方法

- 奇校验实现方式:校验位默认为高电平,每检测到1,则状态翻转

- 偶校验实现方式:校验位默认为低电平,每检测到1,则状态翻转

输入数据的校验方法程序

1 | module odd_even1( |

2.UART通信奇偶校验-输出数据的校验方法

- 实现方法:根据异或的定义:相异为1,相同为0。可推出:偶数个1异或的结果为0,奇数个1异或的结果为1。

- 偶校验:将输入数据按位异或

- 奇校验:将输入数据按位异或再取反(与偶校验相反)

输出数据的校验方法程序

1 | module odd_even2( |

RS232通信协议

- RS232是UART的一种,没有时钟线,只有两根数据线。发送数据端口线TX(Transmitter),接收数据端口线RX(Receiverr)。都为1bit位宽。

- 当PC通过串口调试助手向FPGA发送8bit数据时,FPGA通过接收数据端口线RX,从PC接收一位一位的数据,在FPGA内把连续的8bit的一位宽数据拼接成8bit数据。

- 当FPGA通过串口向PC机发送8bit数据时,FPGA通过数据端口线TX,一位一位的传给PC,从最低位到最高位依次发送,最后上位机通过串助手按照RS232协议把数据拼接成8bit数据。

- 串口数据的发送和接受是基础帧结构的,即一帧一帧的发送与接收。每一帧除了中间的8bit有效数据外,还在每帧的开头都有一个起始位,固定为0;在每帧的结束时有一个停止位,固定为1。不包含校验位的情况下,一帧有10Bit。在不发送和接受收的情况下,RX,TX处于空闲状态,且都为高电平。

- 有数据帧传输时,首先会有一个起始位,然后8bit数据位,最后1bit停止位,然后RX,TX继续进入空闲状态,等待下一次数据传输。

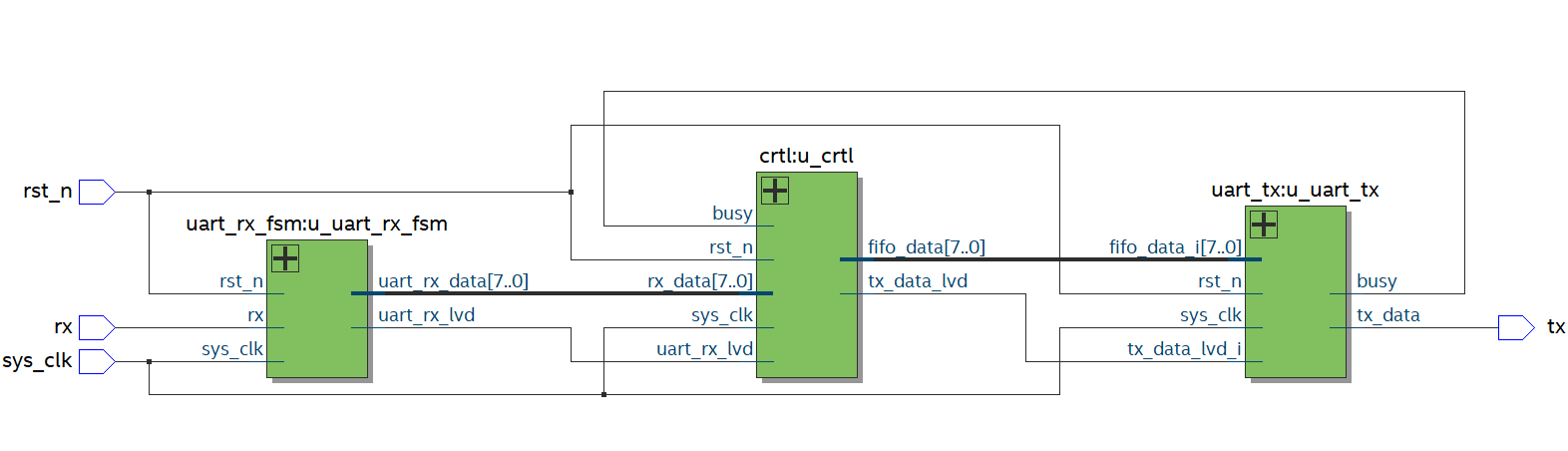

RS232设计思路

- 接收模块RX(Receiverr):首先检测PC上位机发送的输入数据的下降沿,通过两级寄存器将接收到的数据进行同步,再利用一级寄存器来检测输入数据的下降沿。

检测到下降沿后,表示开始接收数据。每计数1bit的中间数,移位寄存器右移一位(相当于保存当前数据)。当bit计数器计数到8,表示有效数据已经接收完毕,当计数到9结束时,接收到结束信号,完成一帧数据的传输,拉高数据有效标志信号,输出有效的并行8bit数据。 - 控制模块(Ctrl):接收接收模块传来的8bit数据,在数据有效标志信号拉高,且FIFO写非满时进行写入FIFO,在TX端非忙且读非空时,进行FIFO读出8bit数据到TX端的操作。

- 发送模块TX(Transmitter):在数据有效信号有效时,开始拉高busy(忙信号),在10bit数据发送完成时,拉低busy(忙信号)。寄存接收控制模块发送来的8bit并行数据,通过拼接符拼接第一bit的低电平0,最高位的bit高电平1;在每bit的计数的第一个baud就把当前bit位的单bit数据发送给PC上位机,进行数据的回环。

接收模块程序

1 | module uart_rx_fsm ( |

控制模块程序

1 | module crtl ( |

发送模块程序

1 | module uart_tx ( |

仿真模块程序

1 |

|

此文章版权归Violet所有,如有转载,请注明来自原作者